電源符號如VDD、VCC、VSS等是電路圖中常見的標識,它們對于理解和設計電路起著關鍵作用。這些符號代表了不同的電源輸入和地線連接,尤其在混合信號電路中,它們的區分和正確使用至關重要。

一、基本電源符號及其含義

VDD:代表數字電路的電源輸入端(DigitalPowerInput)。在數字電路中,VDD是為數字器件提供工作電壓的關鍵引腳。常見的數字電路工作電壓通常為5V或3.3V,但具體電壓取決于器件的設計和應用場景。

VSS:表示數字電路的地(DigitalGround)。作為數字電路的參考電位點,VSS是數字信號的返回路徑。在實際電路中,確保VSS的穩定和低阻抗對于防止數字信號的干擾和噪聲耦合至關重要。

AVDD:是模擬電路的電源輸入端(AnalogPowerInput)。模擬電路通常對電源的穩定性要求較高,AVDD為模擬器件(如運算放大器、模數轉換器等)提供穩定的電源電壓。其電壓值可能與數字電路不同,常見的模擬電路工作電壓可能為5V或其他特定值。

AVSS:代表模擬電路的地(AnalogGround)。與VSS類似,AVSS是模擬信號的參考電位點。由于模擬信號對噪聲敏感,AVSS的布線需要特別注意,以減少數字電路對模擬信號的干擾。

VCC:通常指邏輯電路的電源輸入端(LogicPower)。在一些電路中,尤其是傳統的TTL邏輯電路,VCC常用于表示電源電壓。其具體電壓值可能與VDD相同或不同,這取決于電路的設計和所使用的邏輯家族。

二、混合電路中的電源分配

在混合信號電路(如液晶顯示模塊、帶有模擬和數字功能的SOC芯片等)中,VDD、VCC、VSS、AVDD、AVSS等電源符號的同時出現是常見的。這種設計主要基于以下原因:

電壓等級差異:數字電路和模擬電路可能需要不同的工作電壓。例如,數字電路可能工作在3.3V,而模擬電路可能需要5V或12V等更高的電壓。通過將數字和模擬部分的電源分開(如VDD和AVDD),可以確保每個部分都能獲得合適的電壓,從而保證其正常工作。

防止相互干擾:數字電路通常具有較高的開關速度和較大的電流變化,這可能導致電源和地線上的噪聲。如果數字和模擬電路共享同一電源和地線,這些噪聲可能會耦合到模擬電路中,影響模擬信號的精度和穩定性。通過將數字和模擬電路的電源(VDD和AVDD)和地(VSS和AVSS)分開,可以有效地減少這種相互干擾,提高整個電路的性能。

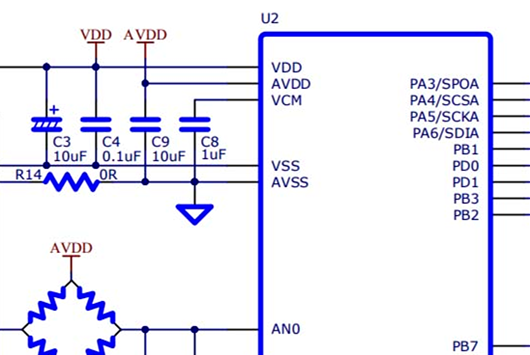

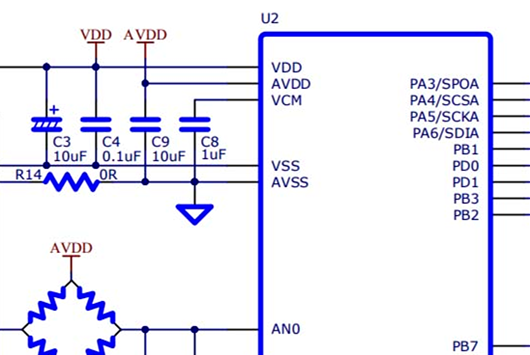

采用多電源為混合芯片供電的典型電路

采用多電源為混合芯片供電的典型電路

三、擴展電源符號及其應用場景

DVDD和DVSS:DVDD(DigitalVDD)和DVSS(DigitalVSS)明確標識了電路中數字部分的電源和地。在復雜的數字系統中,如使用高性能MCU或FPGA的電路,DVDD和DVSS用于為數字邏輯核心供電。它們的電壓值通常與VDD相同,并且需要提供足夠的電流以滿足數字電路的高速開關需求。

AVDD和AVSS:AVDD(AnalogVDD)和AVSS(AnalogVSS)是模擬部分的電源和地。在混合信號芯片中,AVDD為模擬電路塊(如模數轉換器、濾波器等)提供穩定的電源。為了減少數字電路對模擬電路的干擾,AVDD和AVSS應與數字電源和地線分開,并且在布局和布線時應遵循良好的模擬設計實踐。

PVDD和PVSS:PVDD(PowerVDD)和PVSS(PowerVSS)通常用于標識大電流部分的電源和地。在電源管理電路或驅動高功率負載(如電機驅動、LED驅動等)的電路中,PVDD和PVSS用于承載較大的電流。它們的引腳設計通常具有較低的電阻和較大的電流承載能力,以確保高效地傳輸電能并減少功率損耗。

CVDD:CVDD(CoreVDD)一般表示芯片內核的電源電壓。在現代集成電路中,芯片內核可能工作在較低的電壓以降低功耗和提高性能。CVDD為內核邏輯電路供電,并且其電壓值可能與外圍電路的電源電壓不同。

AFVDD:AFVDD(AutoFocusVDD)是針對特定功能(如自動對焦馬達)的電源電壓。在一些帶有自動對焦功能的攝像頭模塊中,AFVDD為自動對焦馬達或其驅動電路提供所需的電壓。這種專門的電源引腳有助于確保自動對焦功能的穩定性和準確性,同時減少對其他電路部分的干擾。

DOVDD和IOVDD:DOVDD和IOVDD通常表示芯片引腳的輸出電壓。在一些具有多種I/O標準或可配置I/O電壓的芯片中,DOVDD和IOVDD用于為特定的I/O引腳組提供電源。它們的電壓值可能與芯片內部的VDD或VCC不同,這取決于芯片的設計和應用場景。

四、電源符號在實際電路設計中的注意事項

電源分配系統規劃:在設計電路時,首先要根據芯片的規格書和電路的需求,規劃電源分配系統。明確每個電源引腳(如VDD、AVDD、PVDD等)的功能和電壓值,并確保電源網絡能夠提供足夠的電流和穩定性。

地線分離與連接:對于混合信號電路,數字地(VSS、DVSS)和模擬地(AVSS)通常在電源入口處分開,并在單點連接到系統的公共地。這種做法可以有效地減少數字信號對模擬信號的干擾,同時保持整個系統的地線參考的一致性。

電源去耦與濾波:為了減少電源線上的噪聲和紋波,通常在電源引腳附近放置去耦電容。這些電容可以濾除高頻噪聲,并為芯片提供短暫的電流緩沖。此外,根據需要,還可以在電源進入電路板的地方添加濾波電路,如LC濾波器或ferritebeads,以進一步提高電源質量。

電源完整性和信號完整性分析:在高速電路設計中,電源完整性和信號完整性分析是不可或缺的。通過使用仿真工具,可以評估電源分布網絡的阻抗、噪聲耦合路徑以及信號線的特性阻抗等參數,從而優化電路布局和布線,確保電路的可靠性和性能。

〈烜芯微/XXW〉專業制造二極管,三極管,MOS管,橋堆等,20年,工廠直銷省20%,上萬家電路電器生產企業選用,專業的工程師幫您穩定好每一批產品,如果您有遇到什么需要幫助解決的,可以直接聯系下方的聯系號碼或加QQ/微信,由我們的銷售經理給您精準的報價以及產品介紹

聯系號碼:18923864027(同微信)

QQ:709211280